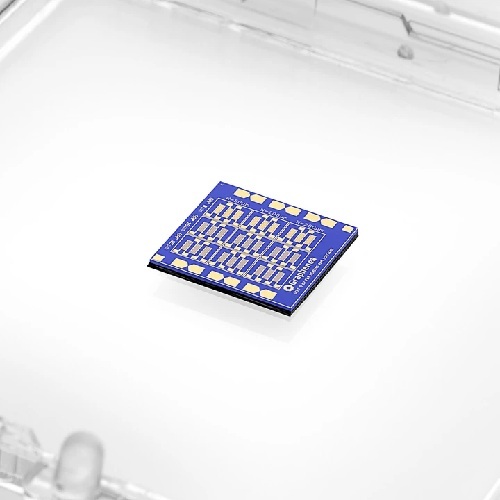

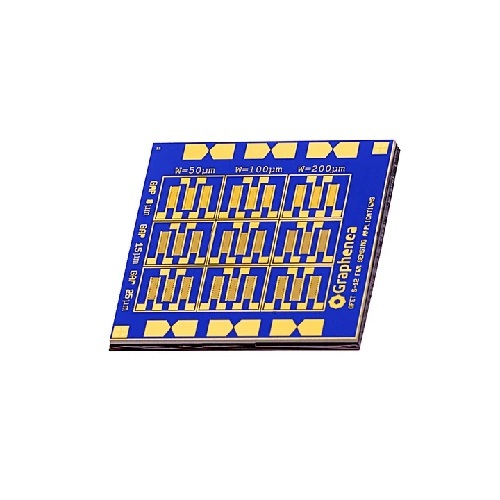

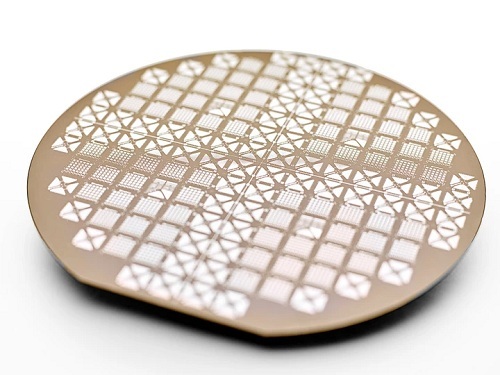

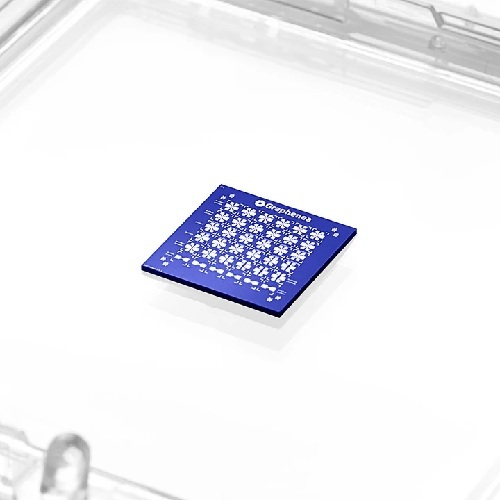

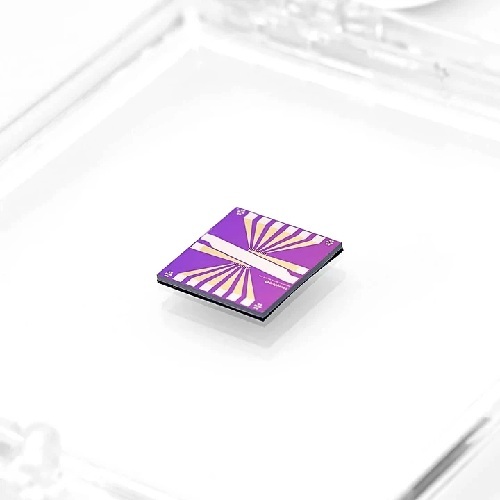

GFET-S20 for Sensing applications

X

GFET-S20 for Sensing applications Price And Quantity

- 01 Number

- 20000 INR/Number

GFET-S20 for Sensing applications Trade Information

- Paypal

- 5 Number Per Day

- 25 Days

- seal pack

- All India

Product Description

Enter Buying Requirement Details

Other Products in 'Sensing Applications' category

|

ULTRANANOTECH PRIVATE LIMITED

All Rights Reserved.(Terms of Use) Developed and Managed by Infocom Network Private Limited. |